مشخصات ساختاری مدارهای منطقی در Verilog

وریلاگ شامل مجموعه عباراتی مربوط به گیتهای منطقی است که معمولا استفاده میشود. شش گیت پایهای اصلی در Verilog شامل AND ، NAND، OR، NOR، XOR، XNOR میباشد. تمامی این گیتها شامل تعدادی ورودی و یک خروجی میباشد. اولین پورت هر گیت خروجی آن و پورتهای بعدی ورودی میباشد. برای مثال یک گیت AND با دو ورودی x1 و x2 و خروجی y بصورت زیر نمایش داده میشود:

and (y, x1, x2);

در جدول شکل ۱ تمام گیت های قابل استفاده در Verilog نشان داده شده است

| نحوه استفاده | نام گیت |

|---|---|

| and(f, a, b, ...) | and |

| nand(f, a, b, ...) | nand |

| or(f, a, b, ...) | or |

| nor(f, a, b, ...) | nor |

| xor(f, a, b, ...) | xor |

| xnor(f, a, b, ...) | xnor |

| not(f, a) | not |

| buf(f, a) | buf |

| notif0(f, a, e) | notif0 |

| notif1(f, a, e) | notif1 |

| bufif0(f, a, e) | bufif0 |

| bufif1(f, a, e) | bufif1 |

شکل ۱

مدارهای منطقی در قالب یک ماژول تعریف میشوند. این ماژول ها شامل محتویاتی هستند که مدار را توصیف میکنند. به عبارتی برای توصیف سخت افزارهای نسبتاً پیچیده باید آنها را به بخشهای کوچکتر تبدیل کنیم، که به هر یک از این بخش های کوچکتر یک ماژول گویند. زمانی که یک ماژول تعریف میشود، الگویی از یک عنصر واقعی ساخته میشود و از این ماژول میتوان به دفعات متعدد استفاده نمود. به فرآیند ایجاد یک نمونه از هر ماژول نمونه سازی و به عنصر ایجاد شده نمونه گویند. هر ماژول دارای ورودی ها و خروجی هایی میباشد که با نام پورت شناخته میشوند. پورت ها در واقع ابزار ارتباط ماژول ها با دنیای بیرون و یکدیگر هستند.

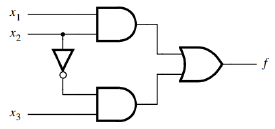

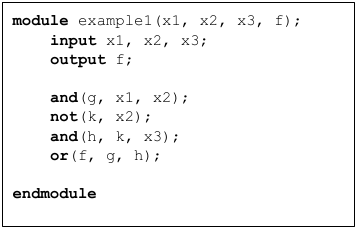

مدار شکل ۲ را در نظر بگیرید. این مدار را میتوان با دستورات Verilog شکل ۳ توصیف نمود. در خط اول یک ماژول تعریف و نام example1 به آن نسبت داده شده و مشخص شده است که در این ماژول چهار پورت وجود دارد. حال برای توصیف این ماژول سه پورت x1 ، x2 و x3 به عنوان ورودی و پورت f به عنوان خروجی تعریف شده است. ساختار اصلی مدار در دستورات خطوط بعدی مشخص شده است. گیت NOT مقدار k=x'2 را به ما میدهد. دو گیت AND مقدار g=x1x2 و h=x'2x3 را تولید میکنند. خروجی دو گیت AND با هم OR میشوند و خروجی f حاصل میشود.

f = g + h

f = x1 x'2 + x2 x3

در نهایت توصیف ماژول تمام میشود.

شکل ۲

شکل ۲

شکل ۳

شکل ۳

پایان تمام دستورات در Verilog با سمیکلون مشخص میشود.

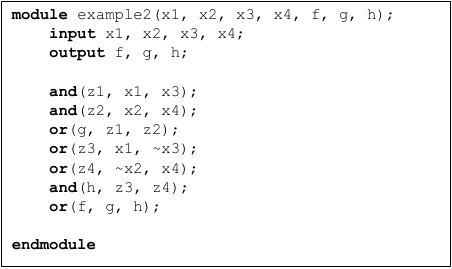

مثالی دیگر از دستورات Verilog در شکل ۴ نشان داده شده است. همانطور که مشخص است این مدار شامل ۴ ورودی x1 و x2 و x3 و x4 و سه خروجی f و g و h میباشد. توابع منطقی در این مدار به صورت زیر پیاده سازی شده است:

g = x1 x3 + x2 x4

h = (x1 + x'3)(x'2 + x4)

f = g + h

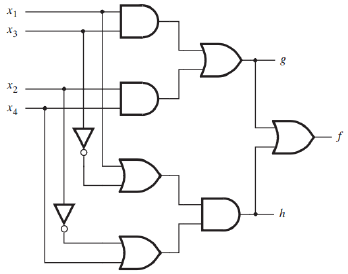

در این مثال به جای استفاده از گیت NOT برای تعریف x'2 و x'3 ، از عملگر "~" در Verilog برای متمم گیری استفاده شده است. بدین ترتیب x'2 به صورت ~x2 نوشته شده است. مدار تولید شده توسط کامپایلر Verilog در شکل ۵ نشان داده شده است.

شکل ۴

شکل ۴

شکل ۵

شکل ۵