مشخصات رفتاری مدارهای منطقی

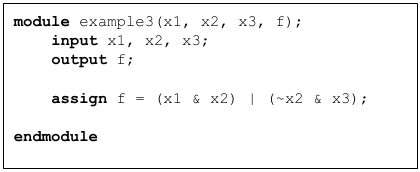

استفاده کردن از گیت ها در Verilog و کار با آنها در طراحی مدارهای بزرگتر و پیچیده تر میتواند خسته کننده و نامطلوب باشد. راه حل دیگر برای توصیف رفتاری یک مدار دیجیتال استفاده از عبارات به صورت برنامه نویسی است. یک راه حل، استفاده از عبارات منطقی برای توصیف مدار است. در شکل ۶ چگونگی استفاده از این عبارات در مدار شکل ۲ نشان داده شده است.

f = x1 x2 + x'2 x3

عملگرهای AND و OR به ترتیب با علامت های “&” و “|” مشخص شدهاند. کلمه کلیدی assign یک مقدار دهی مداوم را بر روی دادهی f مشخص میکند. این دستور همواره فعال است و هرگاه یکی از عملوندهای سمت را دستور تغییر کند، کل عبارت سمت راست مجددا ارزیابی شده و در متغیر سمت چپ قرار میگیرد.

شکل ۶

شکل ۶

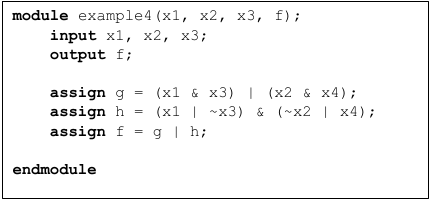

همچنین بر همین اساس، مدار شکل ۵ بصورت دستورات شکل ۷ توصیف میشود.

شکل ۷

شکل ۷

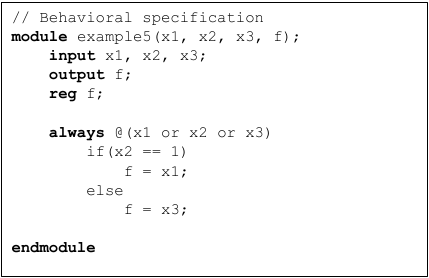

با استفاده از عبارات منطقی میتوان دستورات Verilog را به شیوهای آسان تر نوشت. اما حتی میتوان یک گام بیشتر رو به جلو برداشت و این عمل را آسان تر و قابل درک تر نمود. دوباره مدار شکل ۲ را در نظر بگیرید. این مدار همانند یک مدار مولتی پلکسر ۲ به ۱ است. x1 و x3 داده های ورودی و x2 ورودی کنترل میباشد. خروجی f در این مدار به صورت زیر عمل میکند:

f = x1 if x2 = 1

f = x3 if x2 = 0

این وضعیت در Verilog میتواند در قالب دستور شرطی if-else بیان شود:

if (x2 == 1)

f = x1;

else

f = x3;

دستورات کامل این مدار در شکل ۸ آمده است. خط اول چگونگی ایجاد یک comment را نشان داده است. دستور شرطی if-else نمونهای از دستورات رویهای Verilog است. در ادامه سایر دستورات رویهای، مانند حلقه ها، معرفی میشود.

دستورات رویهای باید درون بلوک ساخت یافتهای بنام always قرار گیرد. بلوک always میتواند شامل یک اعلان و یا مجموعهای از اعلان ها باشد. در طراحی یک مدار در Verilog ممکن است چندین بلوک always وجود داشته باشد که هرکدام بخشی از آن مدار را مدل سازی میکند. یکی از خواص بلوک always این است که تمام دستورات موجود در این بلوک به همان ترتیبی که نوشته شدهاند اجرا میشود. که این در تضاد آن چیزی است که در دستورات مقدار دهی مداوم وجود داشت و تمام دستورات به طور همزمان مورد بررسی قرار میگرفت و هیچ ترتیبی در آن وجود نداشت.

بخشی از بلوک always که پس از علامت “@” درون پرانتز قرار گرفته است را لیست حساسیت مینامند. دستورات درون بلوک always فقط زمانی اجرا میشوند که مقدار یک سیگنال یا تعدادی از سیگنال های درون لیست حساسیت تغییر کند. بدین ترتیب فرآیند یک شبیه سازی ساده شده است؛ چراکه دیگر لازم به اجرای تمام دستورات درون کد در تمام زمان ها نیست. هنگامی که کد Verilog برای سنتز مدار بکار میرود، لیست حساسیت به کامپایلر Verilog میگوید که کدام سیگنال ها میتوانند بصورت مستقیم بر روی خروجی بلوک always تاثیر بگذارند.

اگر قرار است به یک سیگنال مقداری توسط دستورات رویهای نسبت داده شود، باید آن سیگنال به صورت متغیر تعریف شود. این کار با استفاده از کلمه کلیدی reg انجام میگیرد. این نام گذاری به این دلیل انجام گرفت که وقتی مقداری به یک متغیر نسبت داده میشود، شبیه ساز آن مقدار را ثبت کرده (درون یک ثبات ذخیره میکند) و تا زمانی که بلوک always بار دیگر اجرا نشود، مقدارش تغییر نمیکند.

شکل ۸

شکل ۸

توصیفات رفتاری مدارهای منطقی تنها رفتار آن مدار را تعریف میکند. نرم افزارهای سنتز مدار، از این مشخصات برای ساخت مدار واقعی استفاده میکنند. ساختار دقیق از مدار سنتز شده به تکنولوژی استفاده شده در آن بستگی دارد.